## **Computer Graphics Software & Hardware**

NBAY 6120

Lecture 6

Donald P. Greenberg

March 16, 2016

#### Recommended Readings for Lecture 6

- Mike Seymour. "The State of Rendering, Part 1," fxguide.com, July 15, 2013. FXGuide.

- Mike Seymour. "The State of Rendering, Part 2," fxguide.com, July 17, 2013. FXGuide.

#### Why Is It Important?

- 99% of our information intake is pictorial through our eyes

- Educational Modules

- Entertainment

- Games

- Advertising

- Medical

- Computer Aided Design

- Data Visualization

#### **Cornell in Perspective Film**

#### 1972

Program of Computer Graphics, Cornell University

# SCIENTIFIC AMERICAN

COMPUTER GRAPHICS IN ARCHITECTURE

ONE DOLLAR

May 1974

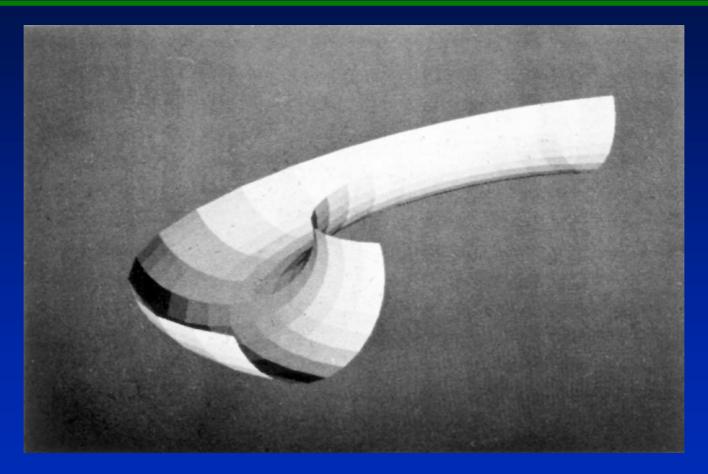

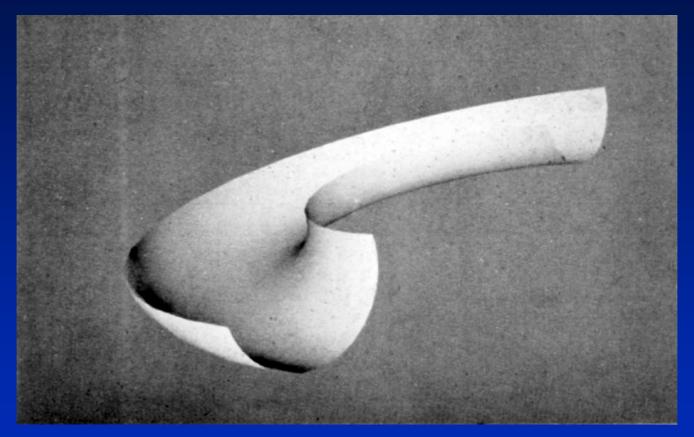

#### **Gouraud Flat Polygon Shading** 1972

Each polygon is shaded based on a single normal.

Gouraud Thesis

Each pixel is shaded by interpolating intensities computed in each of the polygon's vertices.

Gouraud Thesis

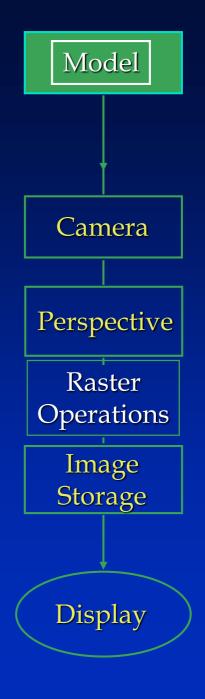

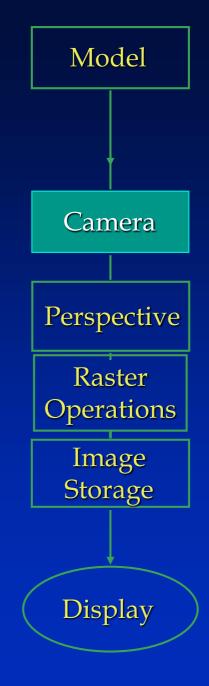

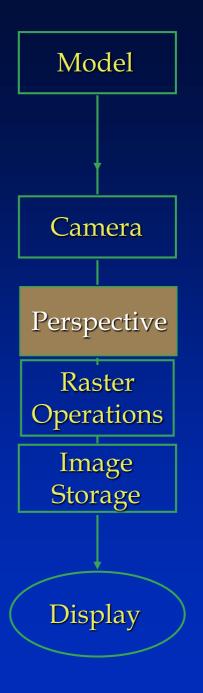

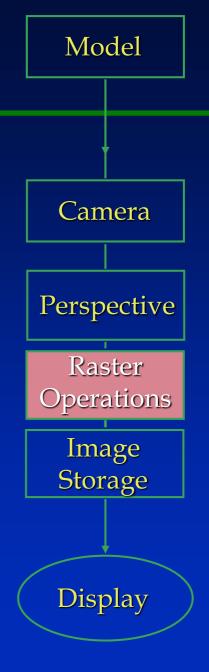

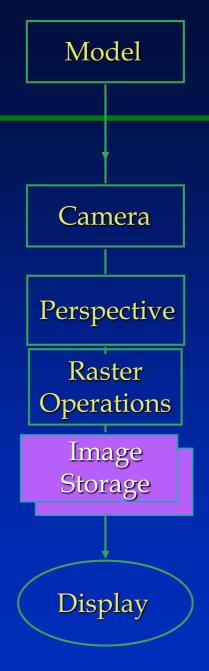

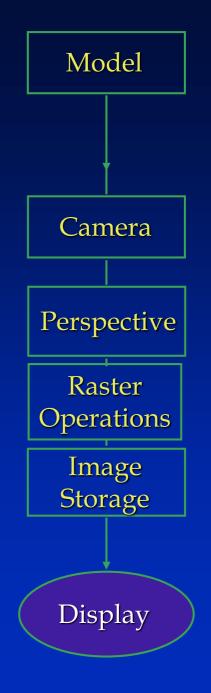

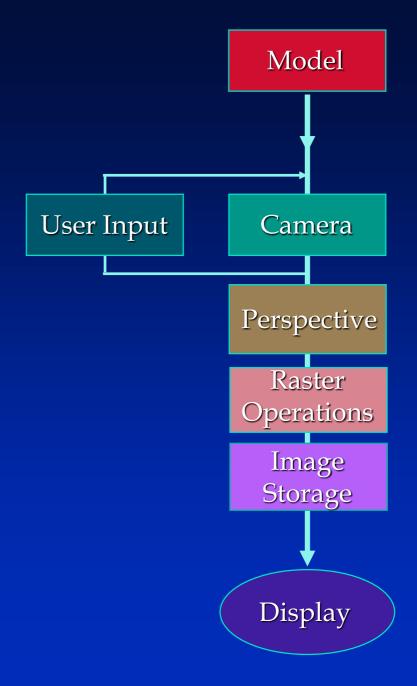

#### Model

Environment

Geometry & topology

Material properties

- >Color, reflectance, textures

- >(Cost, strength, thermal properties)

Lighting

Geometry & position

Intensity, spectral distribution

Direction, spatial distribution

#### Camera

- Viewer Position

- Viewer direction

- Field of view

Wide angle

Telephoto

Depth of focus

Near

Far

# Perspective Transformation

Perspective transformation

Matrix multiplication (4 x 4)

• Clipping objects outside of the field of view

Culling back-facing surfaces

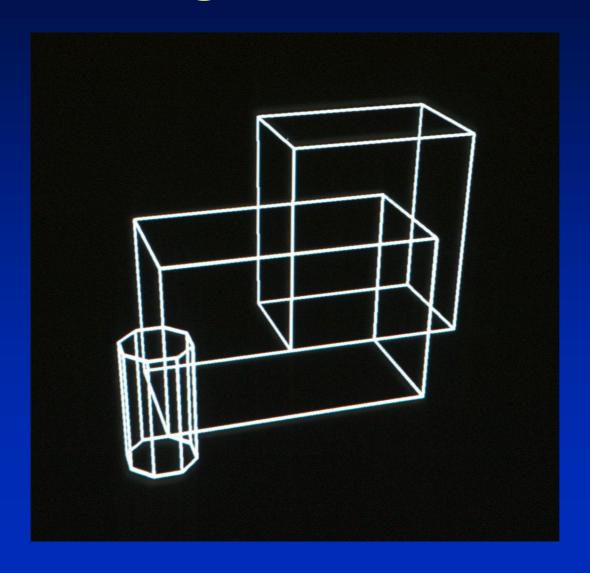

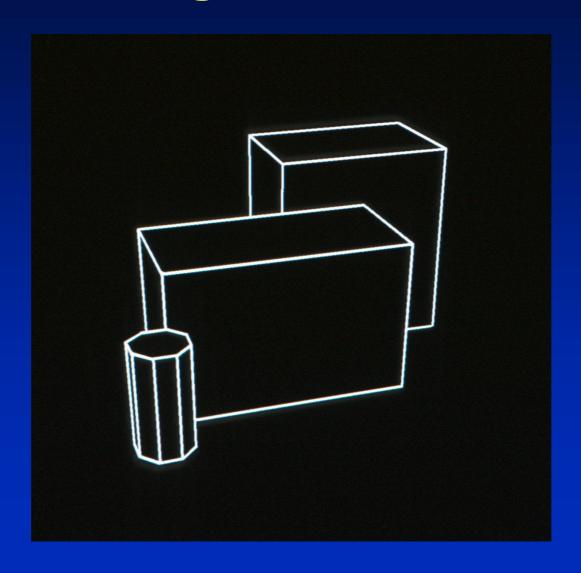

## **Hidden Line Algorithm**

## **Hidden Line Algorithm**

## Raster Operations

- Conversion from polygons to pixelsColor computation

- Hidden surface removal (z-buffer)

## Image Storage

Typical frame buffer

1280 x 1024 pixels

3 channels (red, green, blue)

1 byte/channel

Total memory

3 3/4 megabytes - single buffer

7 1/2 megabytes - double buffer

## Display

Digital to analog conversion

1280 x 1024 resolution

60 frames per second

Total data rate

1 1/4 million pixels

x 3 bytes/pixel

x 60 frames/second

= 225 megabytes/second

= 1.8 gigabits/second

## Direct Illumination

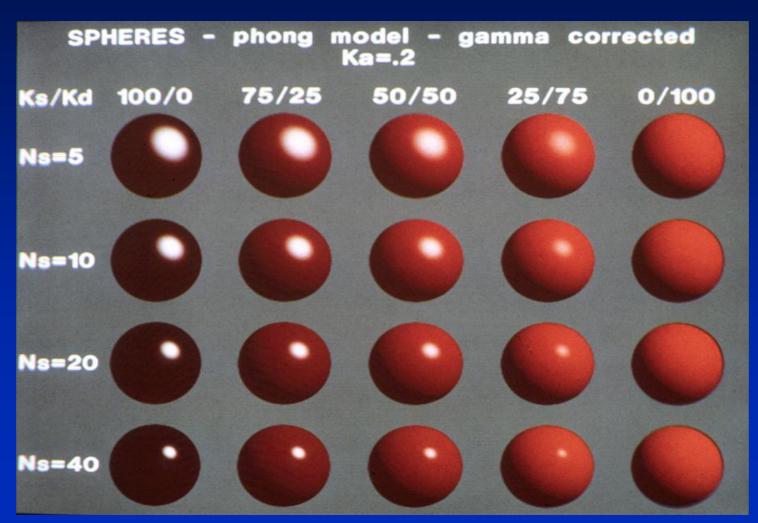

#### Phong Model: Variations of Specular Exponent

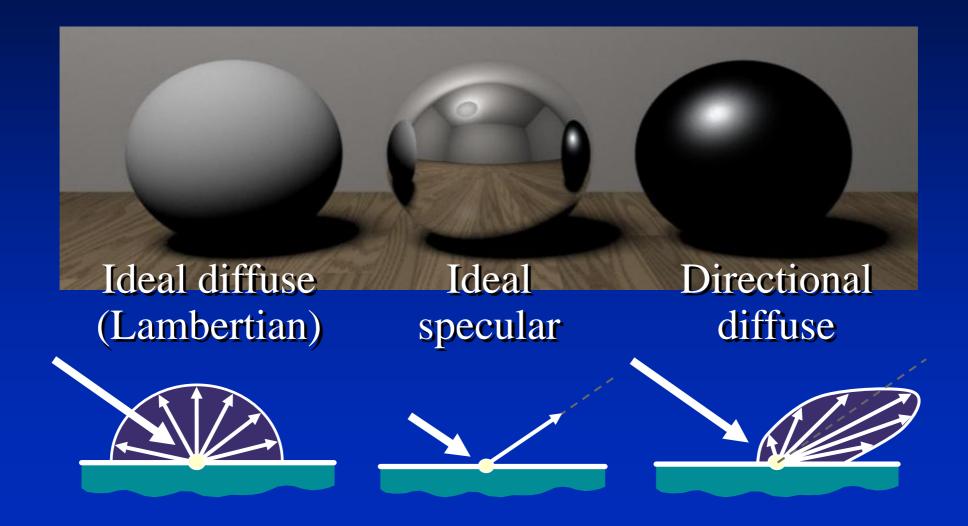

#### Reflectance

#### **Three Approximate Components**

#### **Cook-Torrance Renderings**

#### 1979

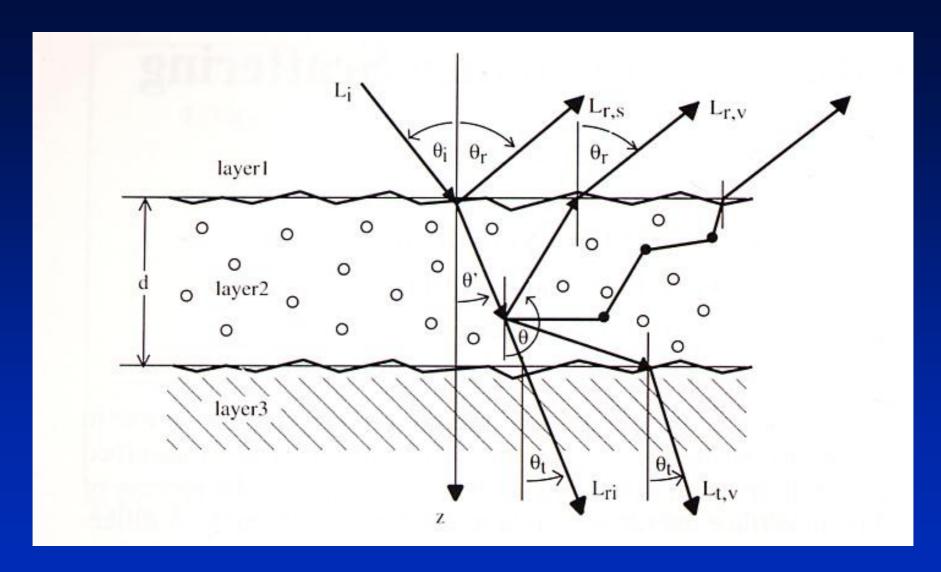

The geometry of scattering from a layered surface

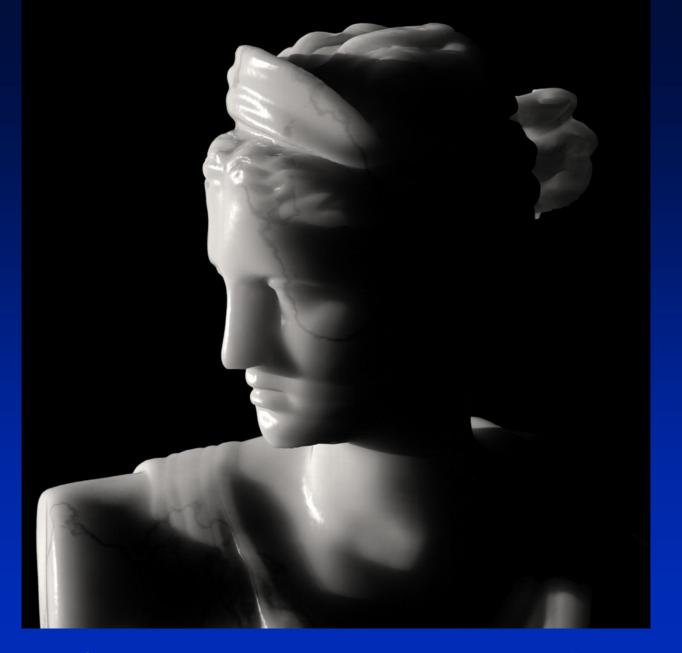

Henrik Wann Jensen, Stephen R. Marschner, Marc Levoy, Pat Hanrahan. "A Practical Model for Subsurface Light Transport," ACM Siggraph 2001, August 2001, Los Angeles, CA, pp. 511-518.

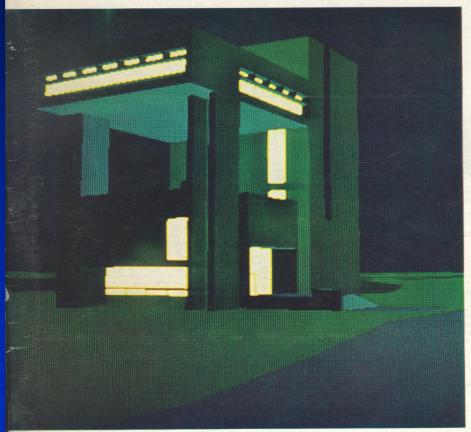

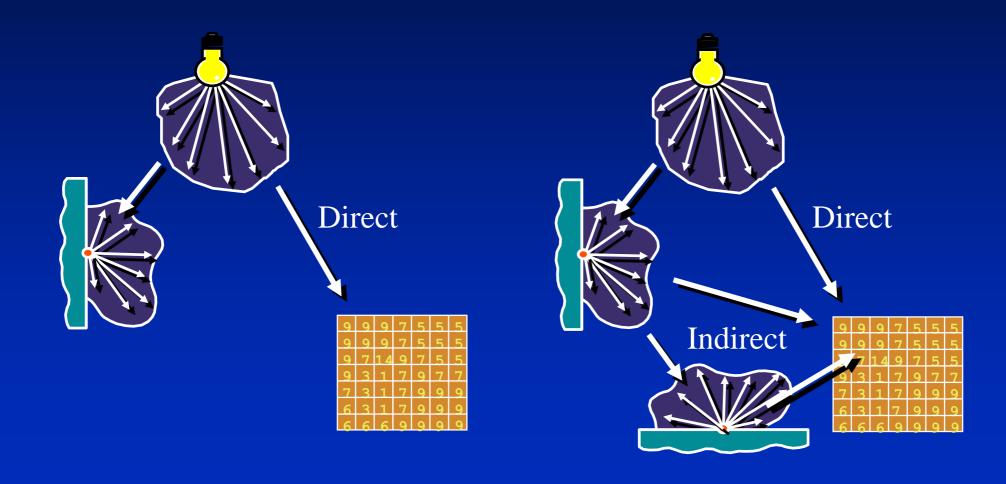

#### **Direct Lighting and Indirect Lighting**

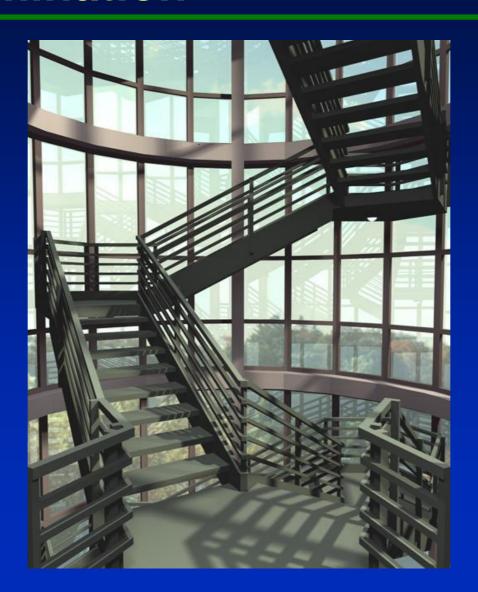

## **Direct Lighting Only**

#### **Global Illumination**

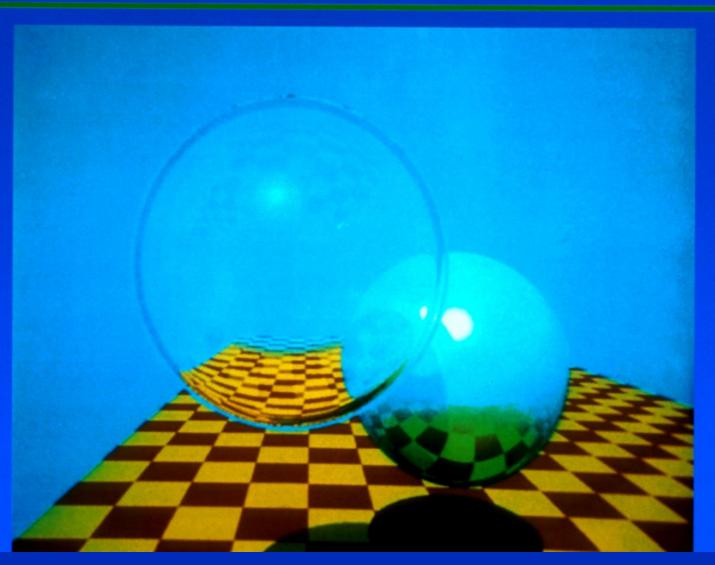

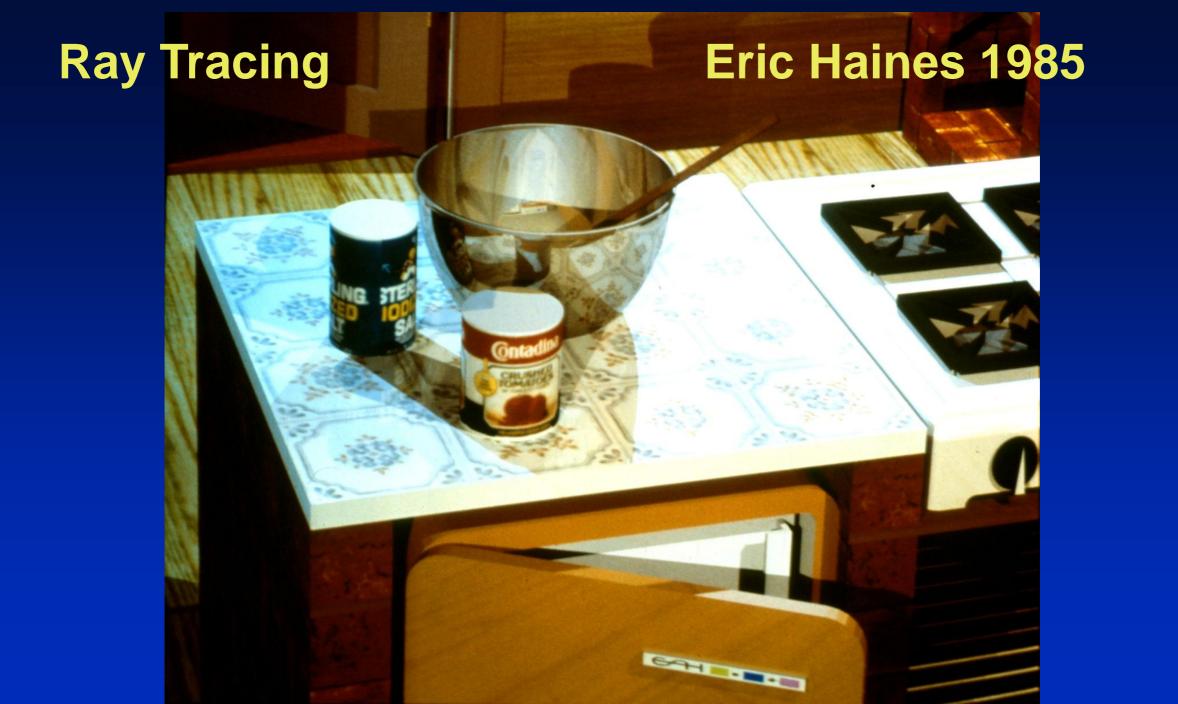

# Ray Tracing *Turner Whitted, 1979*

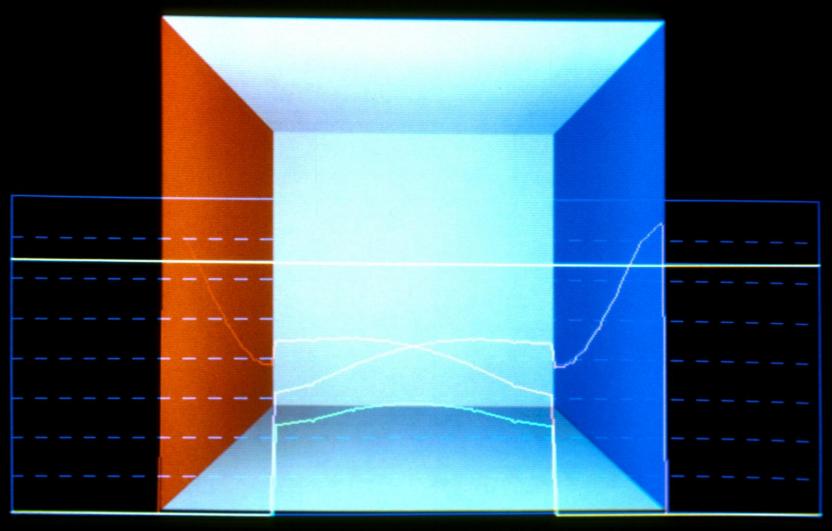

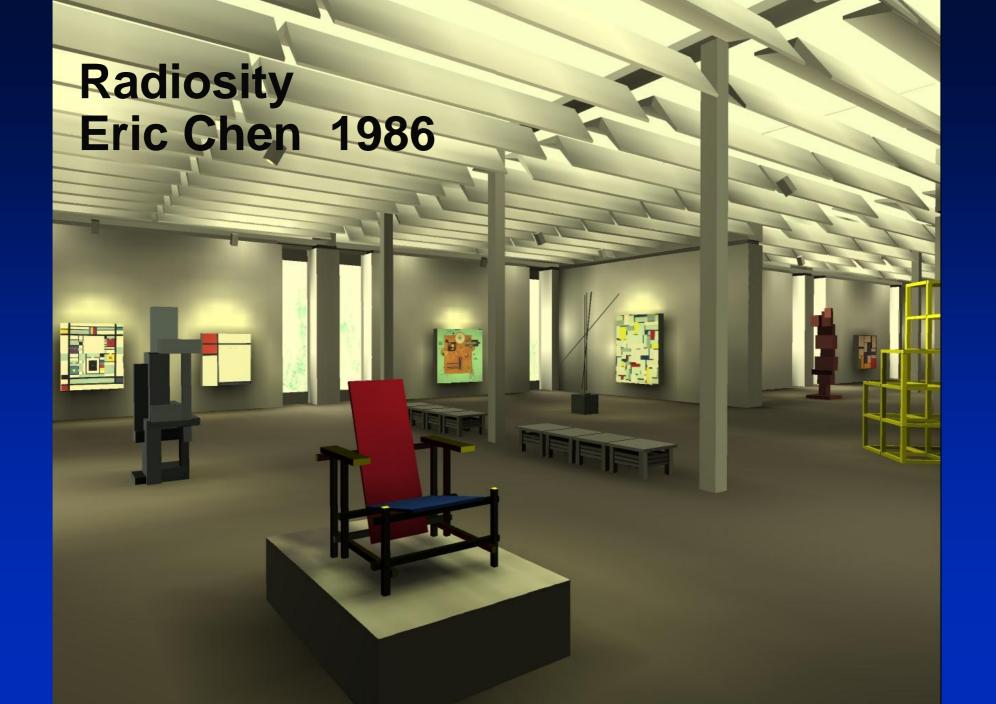

#### Radiosity 1984

## 49 patches per side linear interpolation RGB plot

Radiosity 1990s

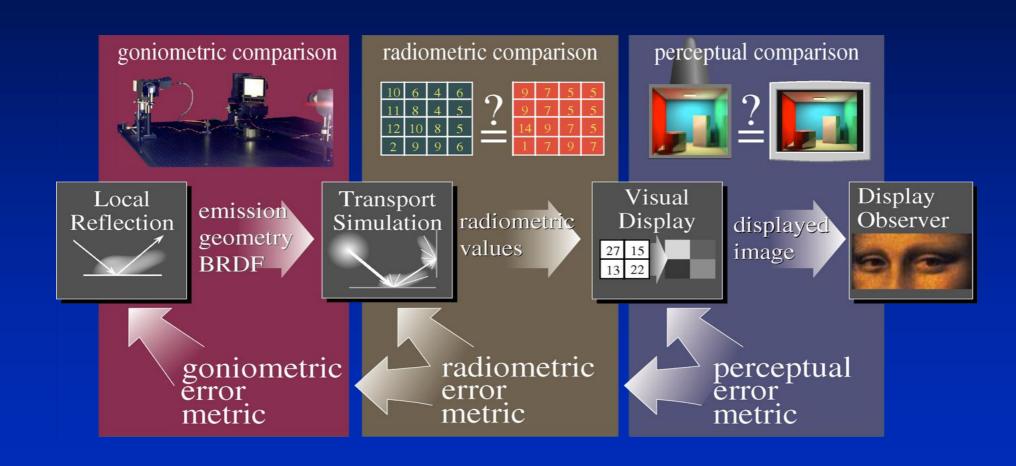

#### Rendering Framework

#### 1997

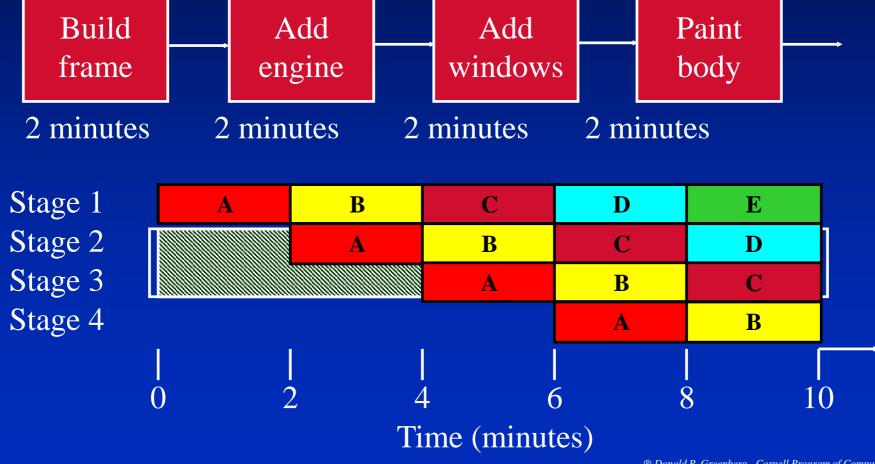

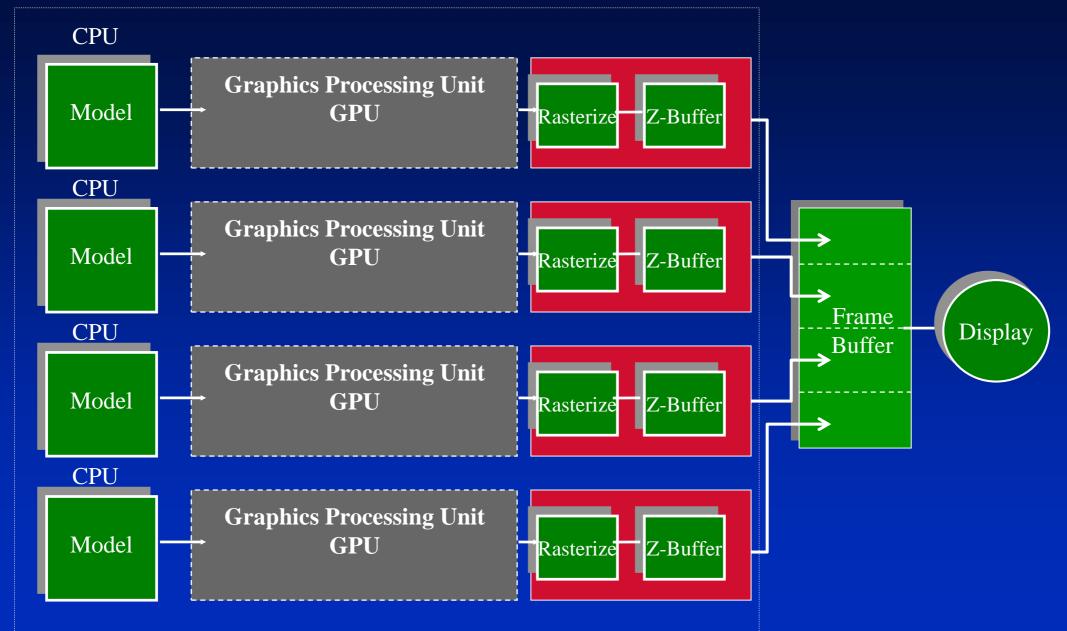

#### **Example: Automobile Pipeline**

Automobile takes 8 minutes to make, but the assembly line makes a car every two minutes.

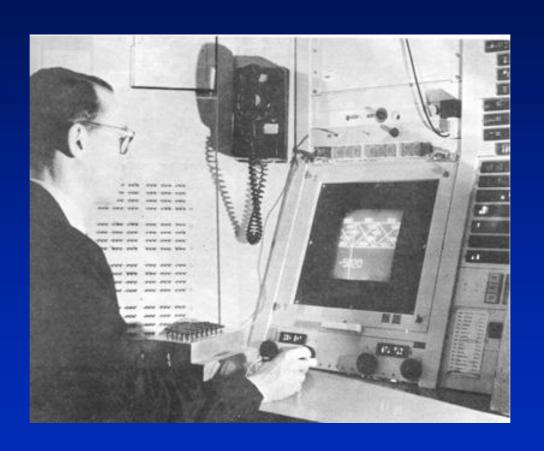

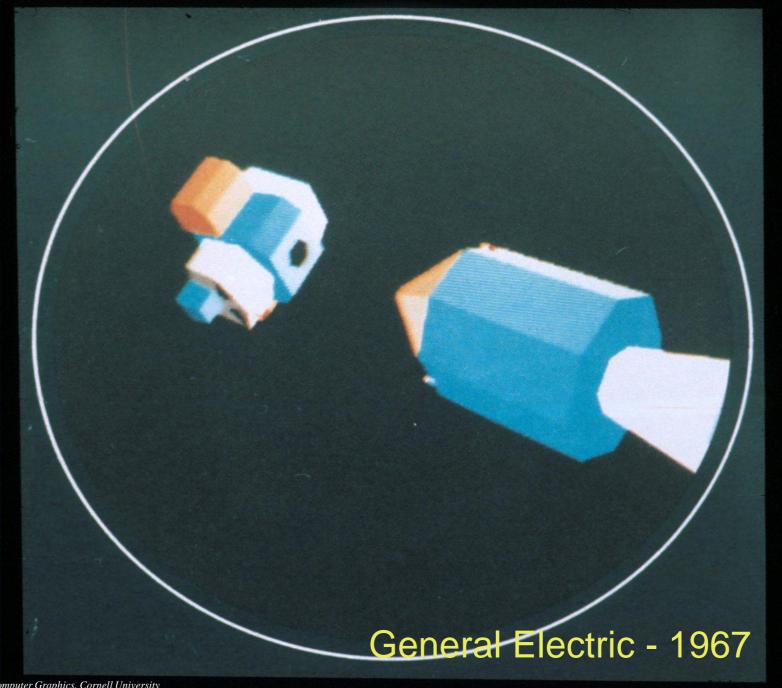

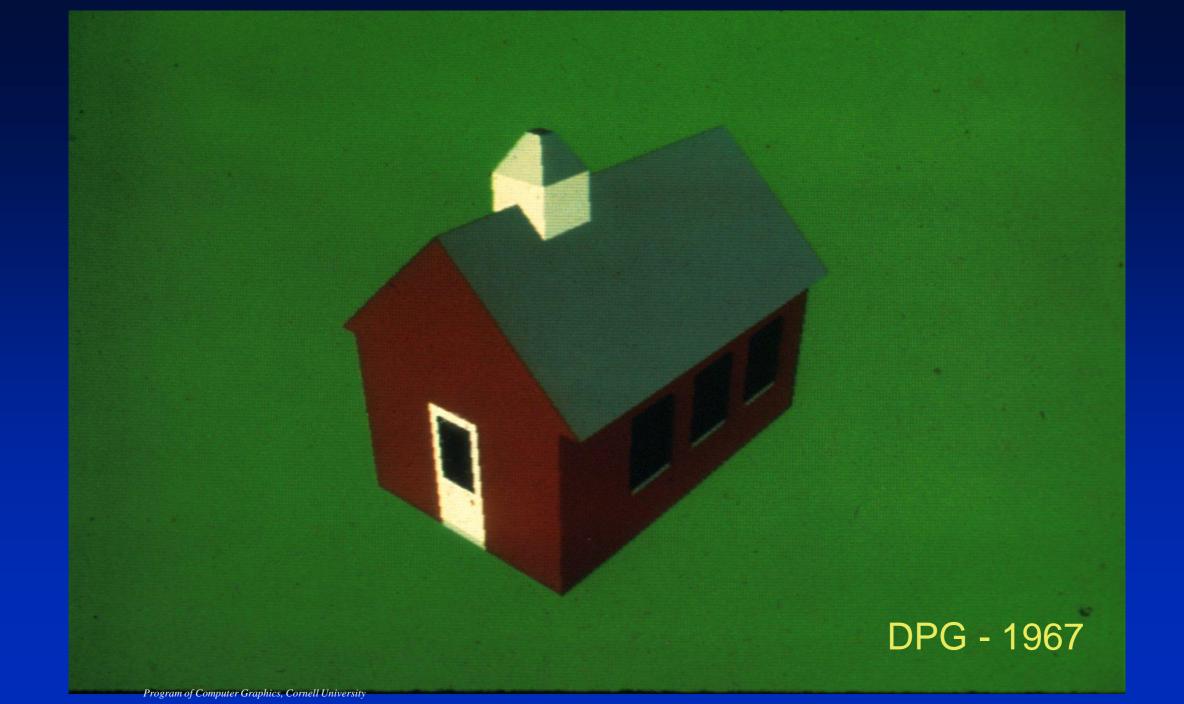

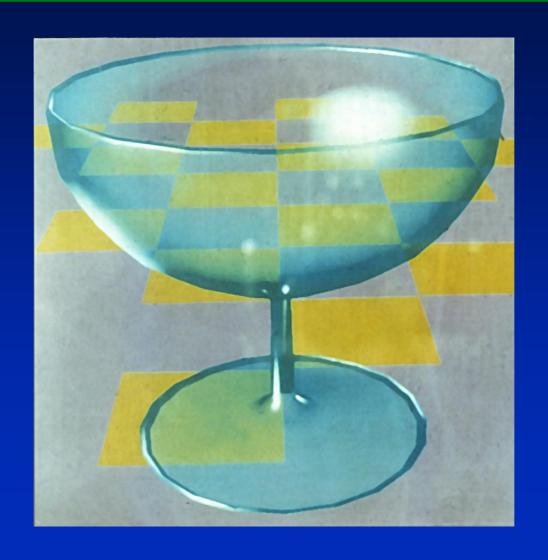

#### **Graphics Hardware circa 1970**

• System used to generate Phong goblet

Graphics Hardware circa 1980

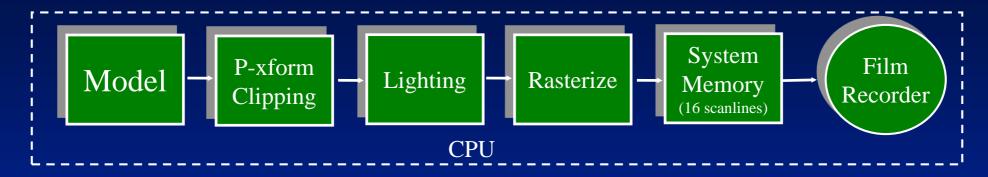

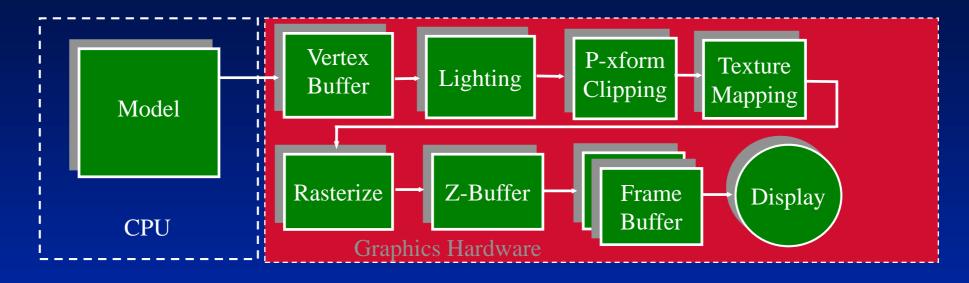

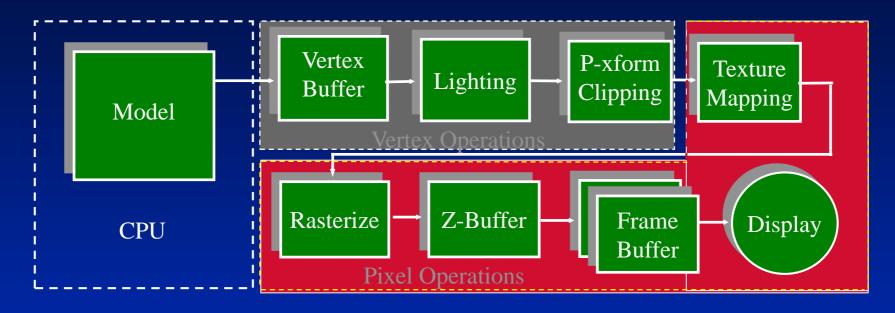

Model P-xform Clipping Lighting Rasterize

CPU

Frame Buffer Display

Graphics Hardware

#### Cost of Memory was Prohibitive

- 512x480x8 bit frame buffer cost \$80,000!

- No z-buffer (at 24 or 32 bits/pixel, it requires even more memory than FB)

- Only single frame buffer

- All work done in CPU until frame buffer(slow!)

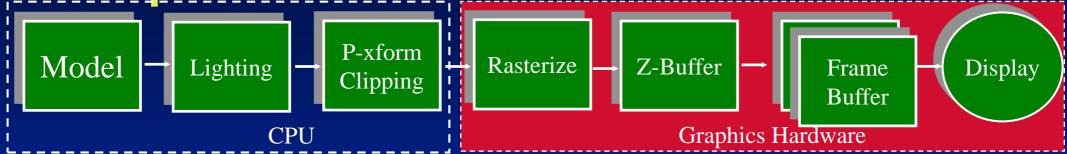

Graphics Hardware circa 1986

- Added Z-Buffer

- Added Double Frame Buffer

- Rasterization and visible surface computations performed in hardware

- Addition of texture mapping units

- With texturing, high resolution detail is possible with relatively simple geometry

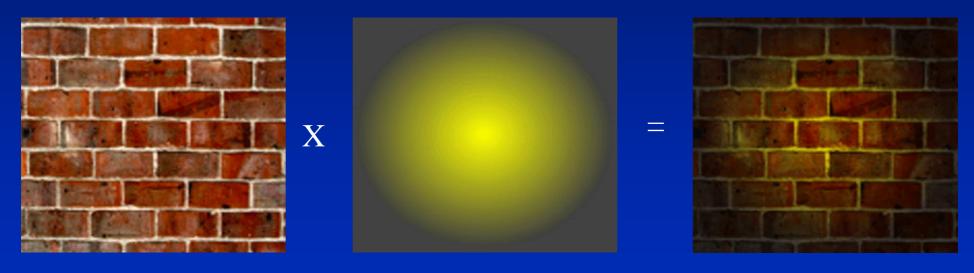

## Multipass Example: Light Maps

• Two separate textures, one for the material's composition, one for the lighting

J.L.Mitchell, M. Tatro, and I. Bullard

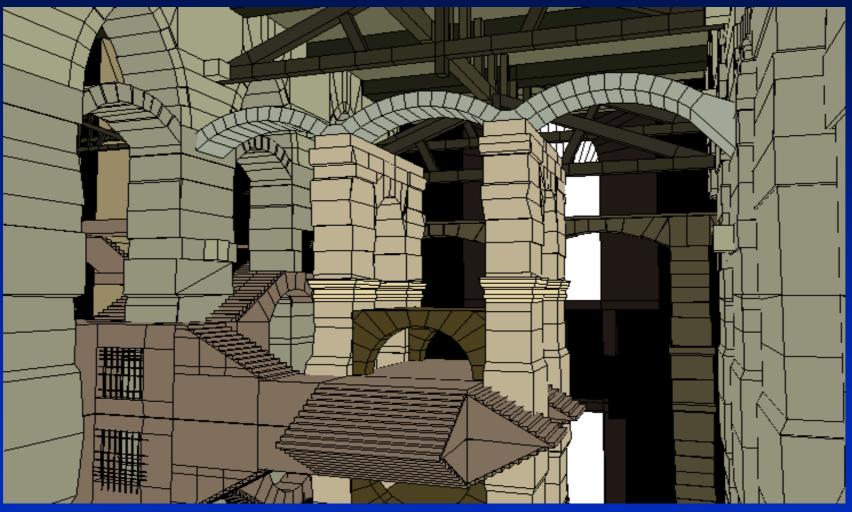

## **Castle's Geometry**

Agata & Andrzej Wojaczek, Advanced Graphics Applications Inc.

# **Reflection Example - Castle**

Agata & Andrzej Wojaczek, Advanced Graphics Applications Inc.

• Vertex buffer (model data) added to reduce bandwidth requirements between CPU and graphics board

#### Graphics Pipeline - 1980's

- M Model

- L Lighting

- P Perspective/Clipping

- S Scan Conversion/Z-buffer

- D Display Storage

- V Video

#### Graphics Pipeline - 2000 +

M L P T S D V

- M Model

- L Lighting

- P Perspective/Clipping

- T Texturing

- S Scan Conversion/Z-buffer

- D Display Storage

- V Video

• Early GPU's performed lighting and clipping operations on locally stored model

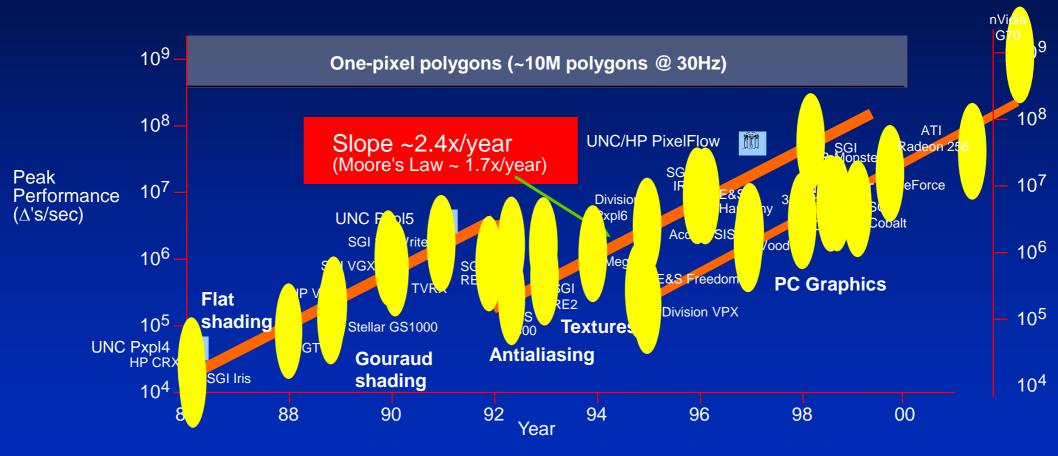

#### **Faster than Moore's Law**

**Graph courtesy of Professor John Poulton (from Eric Haines)**

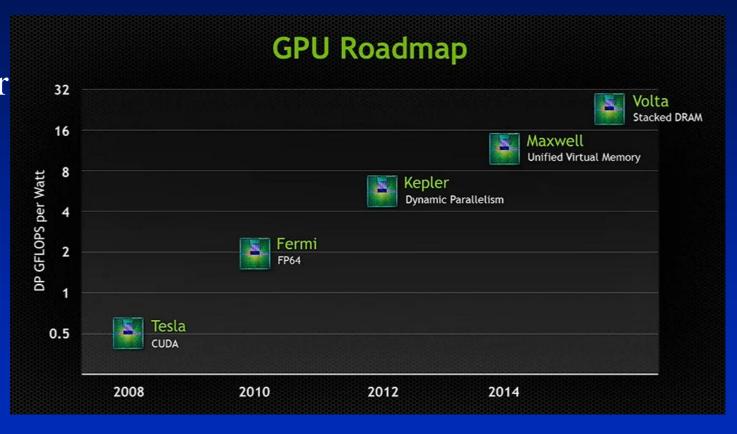

#### nVidia's Kepler Chip

#### 2012

#### **NVIDIA's new Maxwell Chip**

- 6144 processor cores (rumor)

- 20 nm

- Q4 2014

#### **Moore's Law – GPU Transistor Counts**

| Processor       | Transistor count | Date of introduction | Manufacturer | Process | Area    |

|-----------------|------------------|----------------------|--------------|---------|---------|

| R520            | 321,000,000      | 2005                 | AMD          | 90 nm   | 288 mm² |

| R580            | 384,000,000      | 2006                 | AMD          | 90 nm   | 352 mm² |

| G80             | 681,000,000      | 2006                 | NVIDIA       | 90 nm   | 480 mm² |

| R600 Pele       | 700,000,000      | 2007                 | AMD          | 80 nm   | 420 mm² |

| G92             | 754,000,000      | 2007                 | NVIDIA       | 65 nm   | 324 mm² |

| RV790XT Spartan | 959,000,000      | 2008                 | AMD          | 55 nm   | 282 mm² |

| GT200 Tesla     | 1,400,000,000    | 2008                 | NVIDIA       | 65 nm   | 576 mm² |

| Cypress RV870   | 2,154,000,000    | 2009                 | AMD          | 40 nm   | 334 mm² |

| Cayman RV970    | 2,640,000,000    | 2010                 | AMD          | 40 nm   | 389 mm² |

| GF100 Fermi     | 3,200,000,000    | Mar 2010             | NVIDIA       | 40 nm   | 526 mm² |

| GF110 Fermi     | 3,000,000,000    | Nov 2010             | NVIDIA       | 40 nm   | 520 mm² |

| GK104 Kepler    | 3,540,000,000    | 2012                 | NVIDIA       | 28 nm   | 294 mm² |

| Tahiti RV1070   | 4,312,711,873    | 2011                 | AMD          | 28 nm   | 365 mm² |

| GK110 Kepler    | 7,080,000,000    | 2012                 | NVIDIA       | 28 nm   | 561 mm² |

| RV1090 Hawaii   | 6,300,000,000    | 2013                 | AMD          | 28 nm   | 438 mm² |

| GM204 Maxwell   | 5,200,000,000    | 2014                 | NVIDIA       | 28 nm   | 398 mm² |

| GM200 Maxwell   | 8,100,000,000    | 2015                 | NVIDIA       | 28 nm   | 601 mm² |

| Fiji            | 8,900,000,000    | 2015                 | AMD          | 28 nm   | 596 mm² |

- nVidia has designed a series of rackable Tesla servers for very fast computation using parallel sets of their GPU hardware

- They developed a novel programming language (CUDA) to take advantage of their unique hardware architectures. This can be used for many other disciplines

- They now offer a product called Iray which computes photorealistic imagery on a cloud

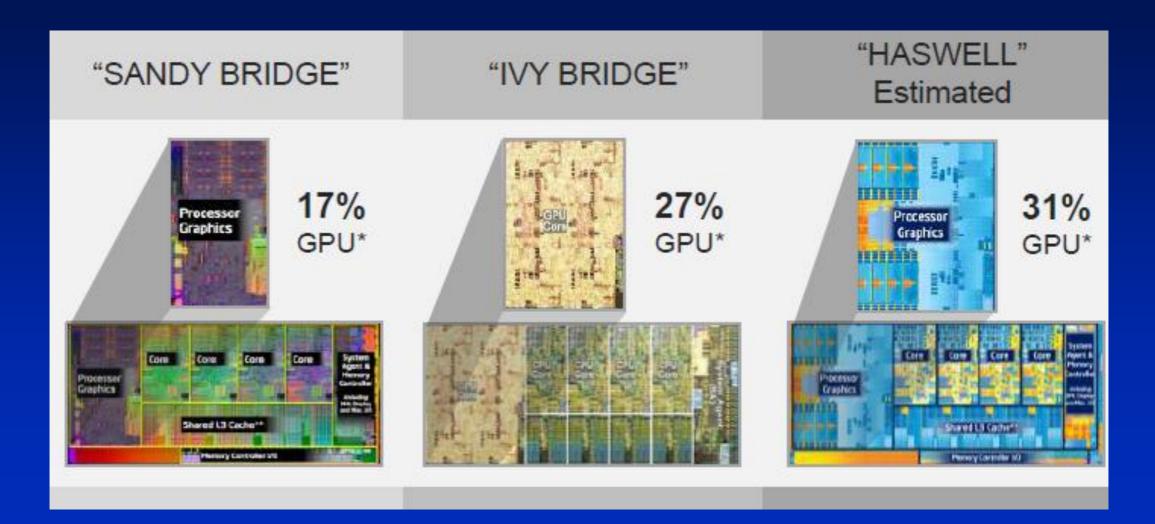

### **Intel – Integrated Graphics**

#### 2013

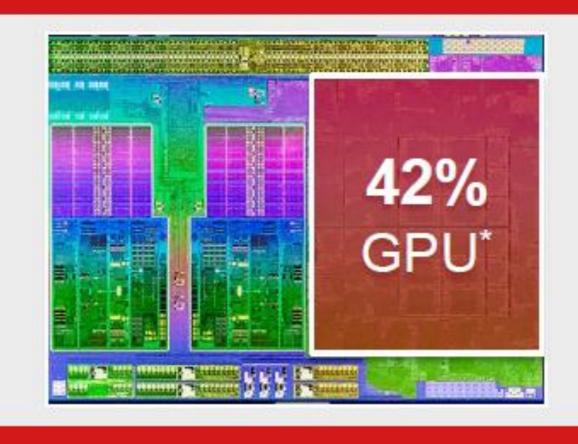

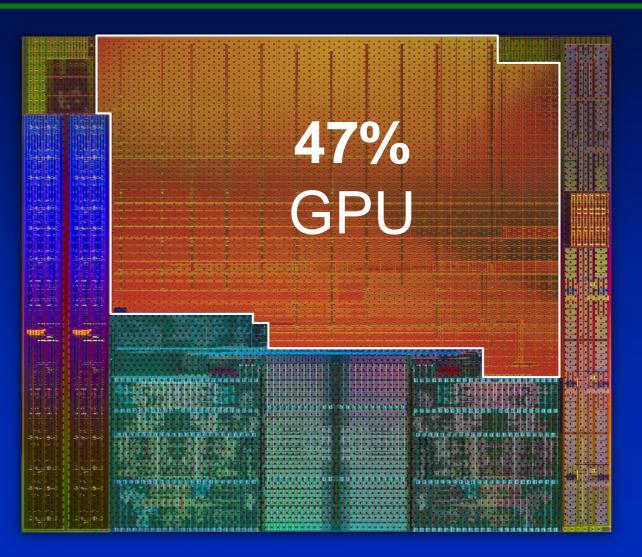

# **AMD – Integrated Graphics**

2013

# ELITE AMD A-SERIES / CODENAMED "RICHLAND"

# **AMD – Integrated Graphics**

2014

- "Kaveri"

- 28 nm

- 47% GPU

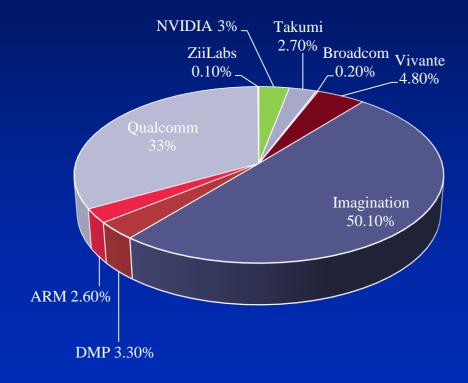

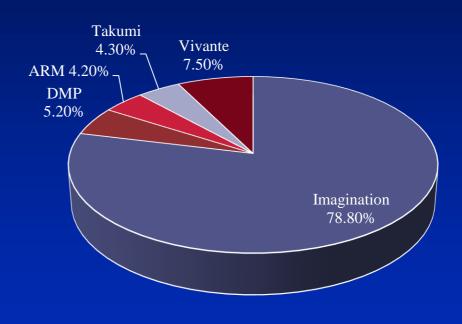

#### **Mobile GPU market share 2013**

#### **All GPU Suppliers**

#### **All GPU IP Suppliers**

# End...